### CS3351 DIGITAL PRINCIPLES AND COMPUTER ORGANIZATION LTPC

### **COURSE OBJECTIVES:**

- To analyze and design combinational circuits.

- To analyze and design sequential circuits

- To understand the basic structure and operation of a digital computer.

- To study the design of data path unit, control unit for processor and to familiarize with the hazards.

- To understand the concept of various memories and I/O interfacing.

### **COMBINATIONAL LOGIC** UNIT I 9

Combinational Circuits – Karnaugh Map - Analysis and Design Procedures – Binary Adder Subtractor – Decimal Adder - Magnitude Comparator – Decoder – Encoder – Multiplexers Demultiplexers

### **UNIT II**

### SYNCHRONOUS SEQUENTIAL LOGIC

Introduction to Sequential Circuits – Flip-Flops – operation and excitation tables, Triggering of FF, Analysis and design of clocked sequential circuits – Design – Moore/Mealy models, state minimization, state assignment, circuit implementation - Registers – Counters.

### **UNIT III**

### **COMPUTER FUNDAMENTALS**

Functional Units of a Digital Computer: Von Neumann Architecture – Operation and Operands of Computer Hardware Instruction – Instruction Set Architecture (ISA): Memory Location, Address and Operation – Instruction and Instruction Sequencing – Addressing Modes, Encoding of Machine Instruction – Interaction between Assembly and High Level Language.

### UNIT IV PROCESSOR

Instruction Execution – Building a Data Path – Designing a Control Unit – Hardwired Control, Microprogrammed Control – Pipelining – Data Hazard – Control Hazards.

UNIT V

### **MEMORY AND I/O**

Memory Concepts and Hierarchy – Memory Management – Cache Memories: Mapping and Replacement Techniques – Virtual Memory – DMA – I/O – Accessing I/O: Parallel and Serial Interface – Interrupt I/O – Interconnection Standards: USB, SATA

### **45 PERIODS**

### **PRACTICAL EXERCISES:**

- 1. Verification of Boolean theorems using logic gates.

- 2. Design and implementation of combinational circuits using gates for arbitrary functions.

- 3. Implementation of 4-bit binary adder/subtractor circuits.

- 4. Implementation of code converters.

- 5. Implementation of BCD adder, encoder and decoder circuits

- 6. Implementation of functions using Multiplexers.

- 7. Implementation of the synchronous counters

- 8. Implementation of a Universal Shift register.

- 9. Simulator based study of Computer Architecture

### **30 PERIODS**

# 9

9

3 0 2 4

9

9

## **COURSE OUTCOMES:**

At the end of this course, the students will be able to:

- CO1 : Design various combinational digital circuits using logic gates

- CO2 : Design sequential circuits and analyze the design procedures

- CO3 : State the fundamentals of computer systems and analyze the execution of an instruction

- CO4 : Analyze different types of control design and identify hazards

- CO5 : Identify the characteristics of various memory systems and I/O communication

TOTAL: 75 PERIODS

## **TEXT BOOKS:**

1. M. Morris Mano, Michael D. Ciletti, "Digital Design : With an Introduction to the Verilog HDL, VHDL, and System Verilog", Sixth Edition, Pearson Education, 2018.

2. David A. Patterson, John L. Hennessy, "Computer Organization and Design, The Hardware/Software Interface", Sixth Edition, Morgan Kaufmann/Elsevier, 2020.

## **REFERENCES:**

1. Carl Hamacher, Zvonko Vranesic, Safwat Zaky, Naraig Manjikian, "Computer Organization and Embedded Systems", Sixth Edition, Tata McGraw-Hill, 2012.

2. William Stallings, "Computer Organization and Architecture – Designing for Performance", Tenth Edition, Pearson Education, 2016.

3. M. Morris Mano, "Digital Logic and Computer Design", Pearson Education, 2016.

### CS3351 - DIGITAL PRINCIPLES & COMPUTER ORGANIZATION

### <u>UNIT II</u>

### SYNCHRONOUS SEQUENTIAL LOGIC

Introduction to Sequential Circuits – Flip-Flops – operation and excitation tables, Triggering of FF,

Analysis and design of clocked sequential circuits – Design – Moore/Mealy models, state minimization,

state assignment, circuit implementation - Registers – Counters.

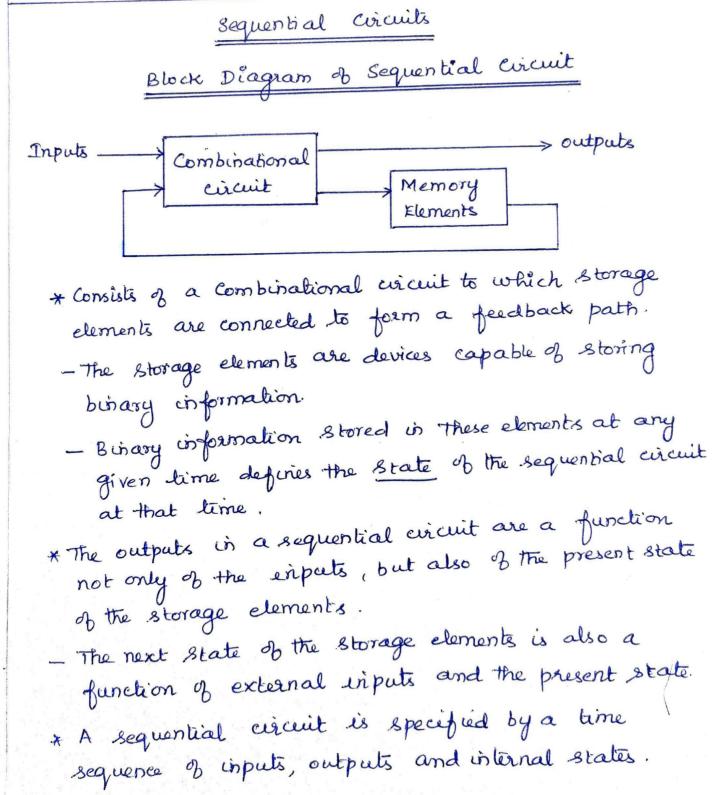

\* employs signals that affect the storage elements only at discrete instants of time. \* Synchronization is achieved by a timing device called a clock generator that provides a periodec train of clock pulses. A Use clock pulses in the inputs of storage elements called clocked sequential circuits. -> The storage elements used in clocked sequential arcuits are called flip-flops. \* A flip-flop is a binary storage device capable of storing one bit of information. Synchronous clocked sequential Circuit >outputs Combinational Inputs circuit Flip-flops clock pulses diagram of clock pulses Timing \* The outputs can come either from the combinational circuit on from the flip-flops on both \* The flip-flops receive their inputs from the combinational circuit and also from a clock signal with pulses That occur at fixed intervals of time. -> The state of the flip-flops can change only during a clock pulse transition.

- \* When a clock pulse is not active, the feedback loop is broken because the flip-flop outputs cannot change even if the outputs of the combinational cricuit driving their inputs change in value.

- -> The transition from one state to the next occurs only at predetermined time intervals dictated by the dock pulses.

| S-No | Synchronous sequential circuits                                                       | Asynchronous Sequential citatis                                                        |

|------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 1.   | Memory elements are clocked<br>Flip - flops                                           | Memory elements are either<br>Untdocked Flep-flops or<br>time-delay elements           |

| Q.   | The change in criput signals<br>can affect memory element<br>upon activation of clock | The change in input signals<br>can affect memory element<br>at any instant of time     |

| 2    | signal.<br>The maximum operating<br>speed of clock depends on<br>time delays involved | Because of the absence of clock,<br>it can operate faster than<br>synchronous circuits |

| 4.   | Easier to design                                                                      | More difficult to design                                                               |

Storage Elements

1. Latches 2. Flip-flops

\* A flip-flop is a binary storage device capable of storing one bit of information.

\* can maintain a binary state in definetely until directed by an input signal to switch states.

- Types based on i) the number of inputs ii) the manner in which the inputs affect the binary state.

<u>Latches</u>:

\* Basic types of flip-flops operate with signal levels

and are referred to as latches. - basic circuits from which all flip-flops are constructed. \* They are not practical for use in synchronous sequential circuits.

## Latches

1 SR Latch 2 D Latch

SR Latch

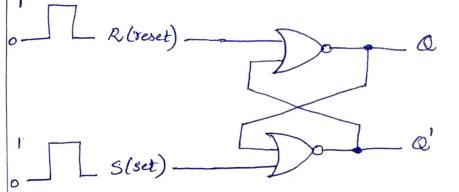

★ The SR latch is a circuit with two cross-coupled NOR gates on two cross-coupled NAND gates.

NOR gates on two cross-coupled NAND gates.

★ Two viputs : S → Set R → Reset

a) <u>SR Latch using NOR gates</u>:

Two states

ii) Reset state: Q=0, Q'=1 +Undefined State: 1/p → both =1, 0/p →0

Logie Diagram

Logic Symbol

Function Table

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                     | 8 | R | Q  | Q |                       |

|-----------------------------------------------------------------------------------------------------------|---|---|----|---|-----------------------|

| 0 0 1 0 (after $S = 1, R = 0$ )<br>0 1 0 1 (after $S = 0, R = 1$ )<br>0 0 0 1 (after $S = 0, R = 1$ )<br> | 1 | 0 | 1  | 0 | ( set state           |

| 0 1 0 1<br>0 0 0 1 (after $s = 0, R = 1$ ) $\begin{cases} \text{Reset State} \\ \end{cases}$              | 0 | 0 | 20 | 0 | (after S=1, R=0)      |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                    | 0 | 1 | 0  | 1 | ? Reset State         |

|                                                                                                           | 0 | 0 | 0  | 1 | (after \$ = 0, R=1) } |

|                                                                                                           |   |   | 0  | 0 |                       |

8=0, R=0

\* Under normal conditions, both viputs of the latch remain at 0 unless the state has to be changed.

\* latch ean be in either the state has to be changed.

\$\frac{1}{2}\$ [atch ean be in either the set of reset state.

\$\frac{1}{2}\$ =1, \$\circ{1}{2}\$ (Set State)

\* \$\frac{1}{2}\$ =1, \$\circ{1}{2}\$ (nput causes the latch to go to the Set state .

\* The \$\frac{1}{2}\$ (nput must go back to 0 before any other changes to avoid the Occeasence of the undefined state.

\$\frac{2}{2}\$ =0, \$R=1\$ (Reset state)

\* \$R=1\$, the latch shifts to reset state .

\* \$R - go back to 0, The circuit remains in the reset state .

\$\frac{2}{2}\$ (Reset state)

\* outputs go to 0, the circuit remains in the reset state .

| •                                                                                                      |                                                                                                         |              |                                                                                                  |

|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------|--------------------------------------------------------------------------------------------------|

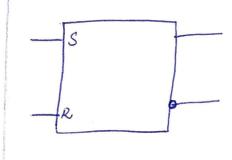

| b) SR Late                                                                                             | h using                                                                                                 | NAND 9       | ates: (S'-R' ratch)                                                                              |

| Logie diag                                                                                             | am                                                                                                      |              | Logic Symbol JR                                                                                  |

| 0 Slset) Do                                                                                            |                                                                                                         |              | - CR                                                                                             |

|                                                                                                        | Function T                                                                                              | able         |                                                                                                  |

|                                                                                                        | S R<br>1 0<br>1 1<br>0 1<br>1 1<br>0 0                                                                  |              | (after S=1, 8=0)<br>(abter S=0, B=1)                                                             |

| changed<br><u>S=0, R = 1 (Set S</u><br>* Apply S=0,<br>* Latch in the<br>* 8 viput 9<br>S=1, R=0 (Rese | tate)<br>vi put causes<br>e set state<br>oes back to 1<br>t state)<br>= 0, the cicul<br>act to 1, the c | , The arcuit | a to go to 1.<br>to remains in the set state.<br><u>reset</u> state.<br>nains in the reset state |

c) SR Latch with Control Input Logic diagram 3.4 S 0 C 0 R Function Table C S R Next State of Q No change X 0 X No change 0 ' 0 Q = 0, Reset State 0 Q = 1, Set state 0 Indeterminate 1 \* SR Latch with two additional NAND gates \* control viput c acts as an enable signal for the other boo viputs. <u>C=0</u> NAND > logec 1 \* The circuit remains in its current state \* disables the circuit, the output does not change regardless of the values of S and R. <u>C=1</u>: \* information from the S or R input is allowed to affect the SR latch. W)C = 1, S = 0, R = 0i) set state:  $\overline{S}=1, R=0, C=1$ & circuit does not change . ii) Reset State: X S=0, R=1, C=1in ) undefined state / indeterminate condition S= 1, B=1, C=1

D Latch: (Transparent Latch)

\* To eliminate the undesirable condition of the indeterminate state in the SR latch is to ensure that inputs 8 and R are never equal to 1 at the same input.

I done in the D latch.

| Logic diagram                                                                                                                                                                     | Logic Symbol        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

|                                                                                                                                                                                   |                     |

| Function Table                                                                                                                                                                    |                     |

| C D Next state of Q<br>O X No change<br>1 O Q=0, Reset State<br>1 1 Q=1, Set State                                                                                                |                     |

| * Latch has two inputs: D (data) and                                                                                                                                              | c (control)         |

| C=0<br>* The circuit cannot change state "                                                                                                                                        | regardless of the   |

| Value of D.                                                                                                                                                                       |                     |

| c=1 * The D wiput is sampled                                                                                                                                                      |                     |

| D=1:<br>D=1:<br>$Questo 1 \rightarrow$                                                                                                                                            | set state           |

|                                                                                                                                                                                   |                     |

| D=0;<br>* The output Q goes to 0 ~<br>DLatch:<br>* Use as a temporary storage for binary<br>a unit and its environment<br>* Binary information present at the data upput          | information between |

| a unit and its environment.<br>* Buiary information present at the data input<br>* Buiary information present at the data input<br>to any information present when the control un | t of the I latch is |

| * Buildry information present at the south of the control un transferred to the Q output when the control un                                                                      | iput is enabled.    |

# Flip-flops

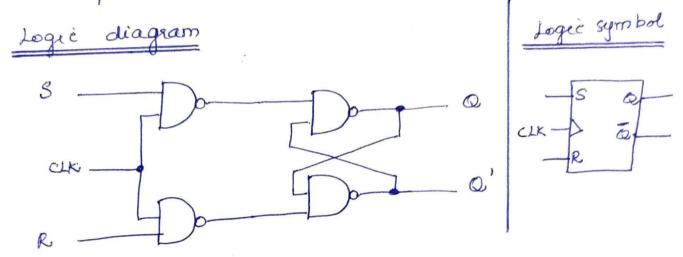

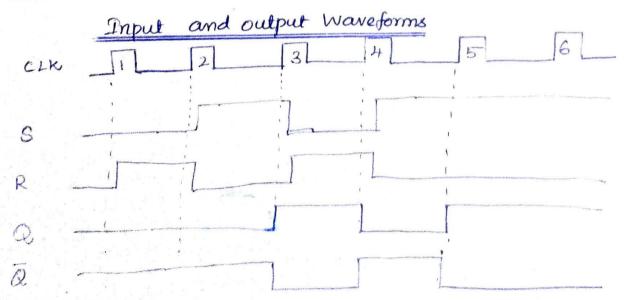

\* The state of a latch on flip-flop is switched by a change in the control input - The momentary change is called a trigger - transition it causes is said to trigger the flip flop. \* A sequential circuit has a feedpack path from the outputs of the flip-flops to the input of the combinational circuit. Latch -> responds to a change in the level of a clock pulse flip-flop-> trigger it only during a signal transition. Clock Response in Latch and Flip-flip (a) Response to positive level (b) Positive-edge response MMM (c) Negative-edge response TTTT. \* A clock pulse goes through two transitions: -> from e to 1 and return from 1 to 0. Edge Triggered Flip-flops: \* change state either at the positive edge or at the negative edge of the clock pulse and is sensitive to its inputs only at the transition of the clock. Types: 1) SR Flip-flop 1) SR Flip-flop 2) J-K Flip - flop 3) D Flip-flop A) T Flip-flop.

1) S.R. Flip- flop :

\* Similar to S-R Latch - enable signal is replaced by clock pulse (CLK) \* The S and R vipuls are called synchronous vipuls because data on the vipuls are transferred to the Flip-Flop's output only on the briggering edge of the clock pulse.

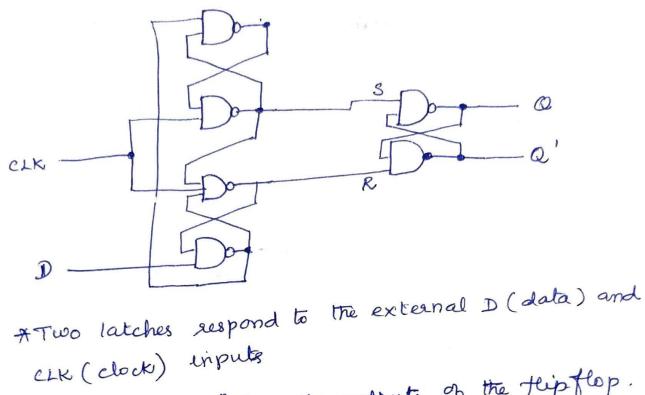

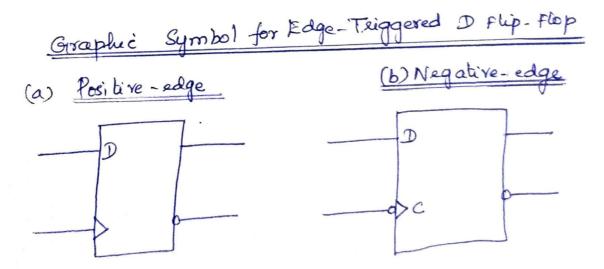

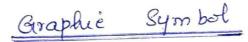

D Flip- flop: \* constructed with two I latches and an inverter D Q D D latch Dlatch (master) C (slave) CLK \* The first latch is called the master and second the slave. - The circuit samples the D input and changes its output a only at the negative-edge of the ak=0: clock When the clock is 0, the output of the inverter is 1. \* The slave latch is enabled and its output Q is equal to the master output Y. - The master latch is disabled because CLK=0, Twhen the input pulse changes to the logic I level, the data from the external D input is transferred > The slave is disabled ous long as the clock remains in the I level. \* The output of the flip-flop can change only during the transition of the clock from I to 0. Graphie Symbol UK-

Construction of an edge-triggered D flip-flop uses Three SR Latches:

\* Third latch provides the outputs of the thip flop.

CLK =0

\* logie I level. \* The output to remain in its present state.

$$\frac{D=0}{\# R=0}$$

$$\frac{R=0}{\# R=0}$$

$$\frac{R=0}{\# Q=0}$$

$$D=1, CLK=1$$

\* When the input clock in the positive-adge-triggered flip-flop makes a positive transition

- the value of D is transferred to Q.

\* A regalive transition from 1 to 0 does not affect the output.

characteristic Table:

| D | QIE | +1)   |

|---|-----|-------|

| 0 | 0   | Reset |

| 1 | 1   | Set   |

a(t+1) -> next state one clock period later.

characteristic Equation:

$$Q(t+1) = D$$

\* The next state of the output will be equal to the value of cipput D in the present state.

\* Most economical and efficient flip-flop construction is the edge-triggered D flip-flop - It requires the smallest number of gates. \* Other lypes of flip-flops ean be constructed by using the D flip-flop and external logic.

$\mathcal{D} = \mathcal{J} \mathcal{Q}' + \mathcal{K}' \mathcal{Q}$

1

$$\underbrace{J=1, \ k=0} \\

* The next clock edge sets the cutput to 1

* Jenpat sets the flip-flop to 1

$D = 0'+0 = 1$

$$\underbrace{J=0, \ k=1} \\

* next clock edge assets the output to 0

* k input assets it to 0

$$\underbrace{J=k=1} \\

* The next clock edge complements the output

$D = 0'$

$$\underbrace{J=k=0} \\

* The clock edge teares the output unchanged

$D = 0.$

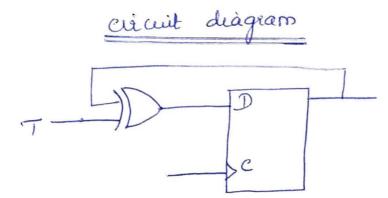

4)  $\underbrace{T = Flip - flop:} \\

* Toggle flip-flop , complementing #up-flop

Using J-k Flip-flop:

* obtained from a J k flip-flop when inputs

fand k are tried together.

$\underbrace{T=0} \\

* J=k=0$

* a clock edge complements the output.

$\underbrace{T=0} \\

* J=k=1$

* a clock edge complements the output.

$\underbrace{T=1} \\

* a clock edge complements the output.

Appliedtioning for designing binary counters$$$$$$$$$$

Using D flip-flop.

\* T Flip-flop can be constructed with a D flip-flop and an exclusive OR gate.

characteristic Table.

| T | Q(t+1) |            |

|---|--------|------------|

| 0 | Q(E)   | Nochange   |

| 1 | Q'(E)  | Complement |

|   |        |            |

$$\frac{T=1}{*} \Rightarrow \mathcal{D} = Q'$$

Analysis of clocked Sequential circuits

\* Analysis describes what a given en cuit will do under certain operation \* The behavior of a clocked sequential critarit is landition determined from the inputs, the outputs and the state of its flip-flops -> The outputs and the next state are both a function of the enputs and the present state.

- \* Analysis

- \* consists of obtaining a table or a diagram for the time sequence 2 inputs, outputs and internal States.

- \* State Equation \* state Table \* state Diagram.

Example:

Step 1.

state Equations

- \* specify the next state as a function of the present state and criputs.

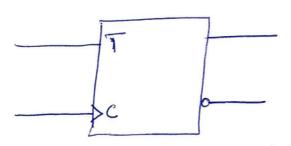

- EX: 2  $\mathcal{D}$  flip-flops  $\rightarrow A, B$ input  $\rightarrow \infty$ output  $\rightarrow \gamma$

- $A(t+t) = A(t) \times (t) + B(t) \times (t)$   $B(t+t) = A'(t) \times (t)$  $Y(t) = [A(t+t) + B(t+t)] \times (t)$

(t+1) > next state of the flip-flop one clock edge later. \* All the variables in the Boolean expressions are a Junction of the present state.

$$A(t+t) = A x + B x$$

$$B(t+t) = A'(x)$$

$$Y = (A + B) x'$$

Present state -> states of flip-flops Aand B at any given time t input -> a value of x for each possible present state.

rext state → states of the flip. flops one clock cycle later at time t+1

output -> value of y at time t for each present state and vipat condition.

| Preser | it state | Input            | Ne | xt state | output |

|--------|----------|------------------|----|----------|--------|

| A      | B        | x                | /  | 4 B      | y      |

| 0      | 0        | 0.               | 0  | 0        | 0      |

| 0      | D        | , I,             | 0  | 1        | 0      |

| D      | [2]      | - 0 <sup>1</sup> | 0  | 0        | . 1    |

| b      | . 1      |                  | 1  | Y        | 0      |

| ř      | 0        | 0                | 0  | 0        | l.     |

| 1      | 0        | I                | 1  | 0        | 0      |

| i      | 1        | 0                | 0  | 0        | 1      |

| 1      | }        | 1                | 1  | 0        | 0      |

\* Listing all binary combinations of present state and inputs \* Next state values are determined from the logec diagram or from the state equations

$$A(t+1) = Ax+Bx$$

$$B(t+1) = A^{1}x$$

$$Y = Ax^{1}+Bx^{2}$$

second form of the State Table m flip-flops ] =) 2 min n viputs J =) 2 rows

| 1 | Present State | Next state |            | output     |       |

|---|---------------|------------|------------|------------|-------|

| - | ×.            | x =0       | $\chi = h$ | $\chi = 0$ | x = 1 |

|   | AB            | AB         | AB         | y          | у     |

|   | 00            | 00         | 01         | 6          | 0     |

|   | 0 1           | 00         | ¥ 1        | 1          | 0     |

|   | 10            | 00         | 10         | i<br>i     | 00    |

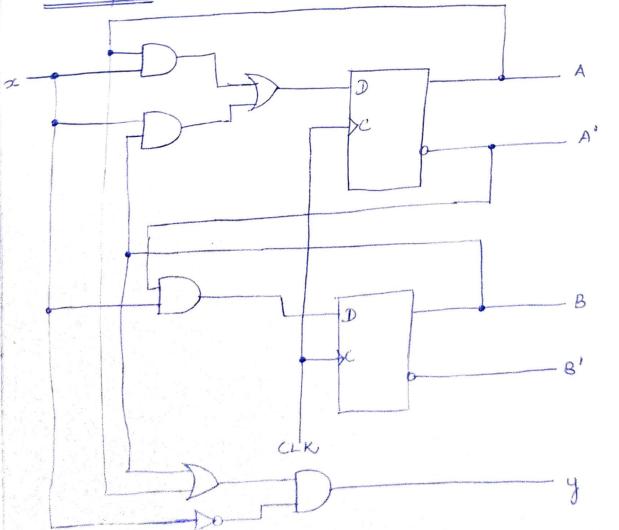

State Diagram \* The information available in a state table can be represented graphically in the form of a state diagram. -> A state is represented by a circle -> The transitions between states are indicated by directed lines connecting the circles.

\* The binary number inside each eicle identifies the state of the flip - flops.

\* The directed lines are labeled with two binary numbers separated by a slash. - input value during the present state is labeled

- the number after the slash gives the output during the present state. with the given isput \* The state diagram gives a pictorial view of state transitions

B the circuit operation

## Output Equations:

\* The past of the combinational circuit that generates external outputs is described algebraically by a set of Boolean functions called output equations.

# Input Equations:

\* The part of the circuit that generates the inputs to flip-flops is described algebraically by a set of Boolean functions called the flip-flop enput equations (excitation equations)

$$DQ = x + y$$

$\int_{name of the flip flop}$

EX:

$$D_{A} = A_{x} + B_{x}$$

$$D_{B} = A'x$$

$$Y = (A+B)x'$$

| a) Analysis with D Flip-flops:                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <u>EX:</u>                                                                                                                                                                                                |

| Input equation : $D_A = A \oplus x \oplus y$                                                                                                                                                              |

| DA > D flip-flop with output A.                                                                                                                                                                           |

| x, y > enputs.                                                                                                                                                                                            |

| i No output equations are given.                                                                                                                                                                          |

| step 1<br>Logic diagram                                                                                                                                                                                   |

| x D D D A<br>y D CLK C                                                                                                                                                                                    |

| <u>stepa</u> <u>State Table</u><br>* one column for the present state for flip-flop A<br>* Two columns for the two inputs<br>* Two column for the next stale & A.<br>* one column for the next stale & A. |

| Present State Inputs Next State                                                                                                                                                                           |

| A xy A                                                                                                                                                                                                    |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

| 0 11 0                                                                                                                                                                                                    |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

|                                                                                                                                                                                                           |

1

\* Next state values are obtained from the state

\* state equation is the same as the input equation.

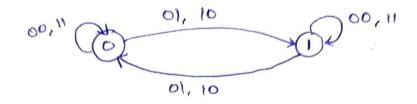

Step 3: State Diagram

\* The circuit has one flip-flop and two states 0,1 \* A slash on the directed lines is not needed because there is no output from a combinational circuit

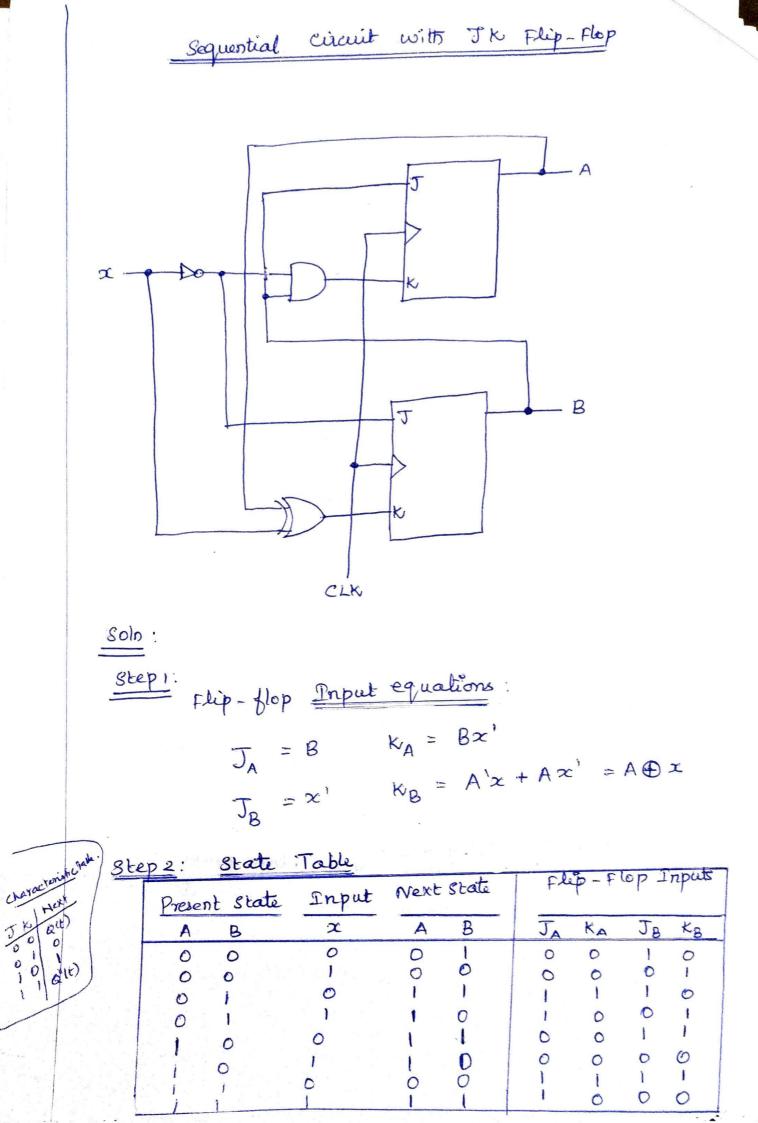

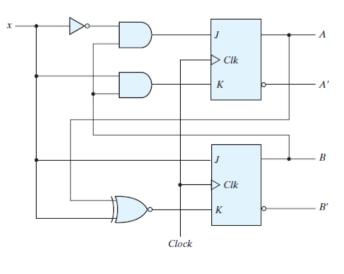

- b) <u>Analysis</u> with JK Flip-Flops: \* To obtain the next state values, - refer corresponding characteristic table or characteristic equation.

- i) \* <u>Procedure</u>:

i) \* <u>Procedure</u>:

i) \* <u>Procedure</u>:

i) The next-state values of a sequential evaluation that uses flup-flops such as JK or T type can be descrived using the following procedure.

1. Determine the flup-flop enput equation in terms of the present state and input variables.

2. List the bihary values of each input equation

3. Use the corresponding flup-flop eharacteristic table to determine the next state values in the state table.

| 1) Next state values using characteristic Table.                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1) Next state values using characteristic Table.<br>* JA, KA<br>JB, KB evaluated using input equations                                                                                         |

| * Next state - evaluated using characteristic Table.                                                                                                                                           |

| J N MEALSING                                                                                                                                                                                   |

| $A \rightarrow J_{A} , M_{B} \qquad \begin{array}{c} 0 & 0 & Q(E) \\ 0 & 1 & 0 \\ 1 & 0 & 1 \\ 1 & 0 & 1 \\ 1 & 0 & (E) \end{array}$                                                           |

|                                                                                                                                                                                                |

| ii) Next state values using state Equations                                                                                                                                                    |

| The purch state values can be obtained the big                                                                                                                                                 |

| evaluating the state equations from the characteristic equation.                                                                                                                               |

| Procedure:                                                                                                                                                                                     |

| 1. Determine the flip-flop input equations in terms                                                                                                                                            |

| of the present state and input inclusion.                                                                                                                                                      |

| 2. Substitute the input aquations into the flip-flop                                                                                                                                           |

| characteristic equation to obtain the state equations<br>3. Use the corresponding state equations to determine the                                                                             |

| 3. Use the corresponding state equations to determine the<br>next state values in the state table.                                                                                             |

| Example Input equations:<br>Step 2: State equations:<br>Step 2: State equations:                                                                                                               |

| <u>Step2</u> State equations :<br>characteristic equation for Jk F/F: Q(t+1)=JQ+KQ                                                                                                             |

| A(t+1) = JA' + K'A                                                                                                                                                                             |

| B(t+t) = JB' + k'B<br>Substitute the input equations in characteristic equations $JA = B$<br>Ka = Bx'                                                                                          |

| Substitute the enput $\Delta f^{a}$<br>$A(t+1) = J_A A' + K_A A \qquad \qquad$ |

| $= BA' + (Bx')'A \qquad k_B \cdot A \oplus x$                                                                                                                                                  |

| BA' + (B + 2) A                                                                                                                                                                                |

| = BA' + B'A + 2A                                                                                                                                                                               |

| A(t+t) = A'B + AB' + AZ                                                                                                                                                                        |

$$B(t+t) = \overline{J}_{B}B' + k_{B}'B$$

$$= x'B' + (A \oplus x)'B$$

$$= B'x' + [Ax + A'x]'B$$

$$B(t+t) = B'x' + ABx + A'Bx'$$

$$\underline{B(t+t)} = B'x' + ABx + A'Bx'$$

$$\underline{Step 3}: State Table$$

$$Refe \quad Previous Table$$

$$\underline{Step 4}: \underline{State \ Diagram}:$$

$$s_{0} \stackrel{()}{0} \stackrel{()}{0} \stackrel{()}{0} \stackrel{()}{s_{2}}$$

$$g_{1} \stackrel{()}{0} \stackrel{()}{0} \stackrel{()}{s_{2}}$$

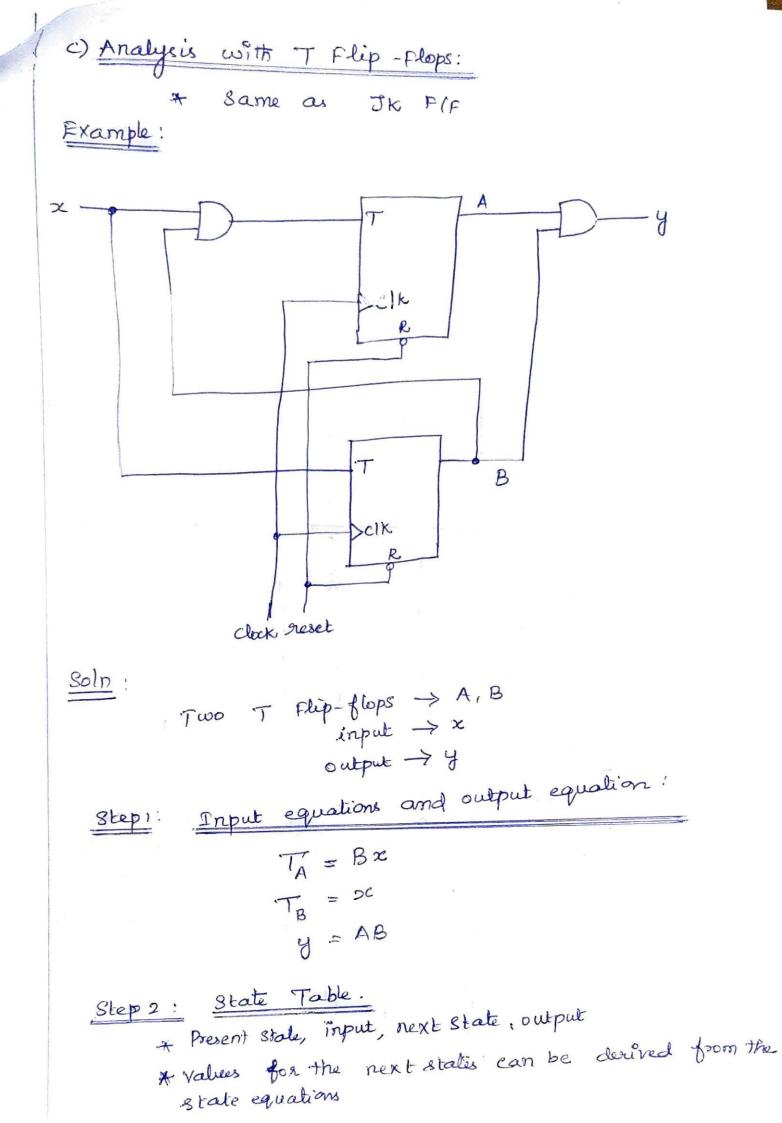

- substitute TA and TB in characteristic ; equation. Q(L+1)=TDQ

$$A(t+1) = T_A A' + T_A A'$$

$$= (BX)A' + (BX)'A$$

$$= A'BX + (B'+X')A$$

$$A(t+1) = A'BX + AB' + AX'$$

$$B(t+1) = T_B \oplus B$$

$$B(t+1) = \chi \oplus B$$

State Table for sequential Circuit with T Flip flops

| Present State | Input | Next Sta | ate Output |

|---------------|-------|----------|------------|

| A B           | x     | A B      | ¥          |

| 0 0           | 0     | 0 0      | 0          |

| 0 0           | F     | 0 1      | D          |

| 0 1           | 0     | 0 1      | Ø          |

|               | 1     | + 0      | ٥          |

| 0             | 0     | 1 0      | 0          |

| 1 0           |       | i t      | 0          |

| 10            | 1     |          | 1          |

| 1             | 0     |          | 1          |

|               | 1     | 0 0      | 1          |

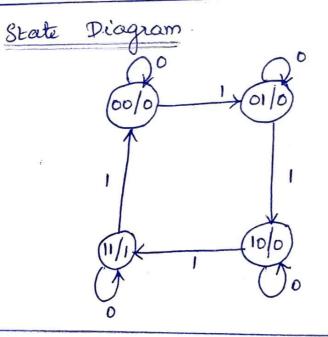

\* OIP depends on the present state only - midependent of 1/p \* Present state / output

= TQ+TQ

before the active edge of the clock.

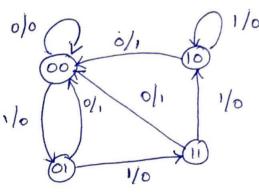

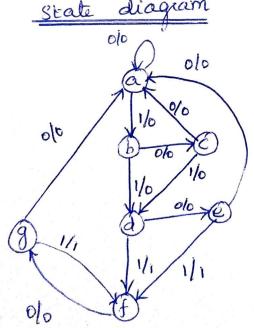

# State Reduction and Assignment

Input sequence: 01010110100; Initial state: a

Step 1: Find the complete sequence \* Each coput of o or 1 produces an output of 0 or 1 - causes the circuit to go to the next state state a a b c d e f f g f g a 1 1 0 1 0 0 input o 0 101 output 0 0 0 0 0 1 1 0 1 0 0 \* The next state is written on the top of the next column. Reduce the number of states Stepa: State Table \* Obtain directly from the state diagram. output Next state Present State  $\chi = 0$ x = 1X=0  $\chi = 1$ 0 0 6 a a 0 0 d C Ь d 0 0 a C 0 f e d 1 f a 0 e t f 1 9 0 9 F a 0 \* Two states are said to be equivalent if - for each member of the set of inputs, they give exactly the same output and send the circuit either to the same state on to an equivalent state.

\* When two states are equivalent - one of them can be removed without altering input-output relationships. i) states e and g are équivalent \* Both goto states a f f outputs o f1

| Reducing the  | sta        | te table |     |       |

|---------------|------------|----------|-----|-------|

|               |            | it state |     | itput |

| Present State | $\chi = 0$ | x=1      | 1=0 | x=1   |

| a             | a          | Ь        | 0   | 0     |

| Ь             | C          | d        | 0   | 0     |

| C             | a          | d        | 0   | 0     |

| d             | e          | ſ        | 0   | ł     |

| e             | a          | f        | 0   |       |

| t             | e          | f        | 0   | 7     |

\* Remove 'g' state and replace it with the equivalent State è'

ii) States of and dave equivalent - state of can be removed and replaced by d

| Reduce                | ed sta                | te Tat               | de<br>= |            |

|-----------------------|-----------------------|----------------------|---------|------------|

| Present state         |                       | state                | 1       | put<br>χ=1 |

| a<br>b<br>c<br>d<br>e | а<br>с<br>а<br>е<br>а | 6 0 0 0 d<br>0 0 0 d |         | 00         |

\* consists of only 5 states Reduced State diagram step 00 olo ta K olo

010

| step 4: List - Input seq  | uance                             |

|---------------------------|-----------------------------------|

| state a a b c d a         | ed de de a                        |

| Input 01010               | 110100                            |

| output 0 0 0 0 0          | 1 0 1 0 0                         |

| * same as the origina     |                                   |

| + Reduced the number of   | statis from seven to five.        |

| State Assignment:         |                                   |

| # Assign unique coded b   | inary values to the scales        |

| * For a circuit with m    | states, the codes must            |

| contain $n$ bits, $2^n >$ | ກາ                                |

| 3 bills -> 8 8            | tates from coo to 111             |

| step 5: Assign binary ra  |                                   |

| * use building coun       |                                   |

| * Ose Gray code           | avsignment                        |

| * Use one-hot about       | Jamen L-                          |

| 한 동물 정말 가지 않는 것이 같아.      | inary State Assignments           |

| Assignment                | 1 Assignment 2 Assignment 3       |

| State Binary              | Giray code One-hot                |

| a 000                     | 000 00001                         |

| b 001                     | 001 00010                         |

| C 010                     | 010 01000                         |

| a 011                     | 10000                             |

| e 100                     | 110                               |

| a sade s cale me b        | it in the code group changes when |

\* Gray code > only one bit in the code group changes when going from one number to the next.

one-hot assignment → one bit is equal to 1 — uses one glip-flop per state \* one-hot encoding leads to simpler decoding logic for the next state and output \* one-hot machines can be faster than machines with sequential binary encoding.

Reduced state Table with Binary Asignment,

|               | Next State |     | oul | put             | _     |

|---------------|------------|-----|-----|-----------------|-------|

| Present State | C          | K=1 | x=0 | $\chi \simeq 1$ |       |

| 000           | 000        | 001 | 0   | 0               | , r . |

| 001           | 010        | 011 | 0   | 0               |       |

| 010           | 000        | 011 | 0   | 0               |       |

| 011           | 100        | 011 | 0   | Y               |       |

| 100           | 000        | 011 | 0   | 1               |       |

#### **DESIGN PROCEDURE**

- Design procedures or methodologies specify hardware that will implement a desired behavior.

- The design effort for small circuits may be manual, but industry relies on automated synthesis tools for designing massive integrated circuits.

- The sequential functionality that is to be implemented by the synthesis tool.

- Illustrate manual methods using D, JK, and T flip-flops.

- ✓ The design of a clocked sequential circuit starts from a set of specifications and culminates in a logic diagram or a list of Boolean functions from which the logic diagram can be obtained.

- → The first step in the design of sequential circuits is to obtain a state table or an equivalent representation, such as a state diagram.

- $\rightarrow$  A synchronous sequential circuit is made up of flip-flops and combinational gates.

- → The design of the circuit consists of choosing the flip-flops and then finding a combinational gate structure that, together with the flip-flops, produces a circuit which fulfills the stated specifications.

- → The number of flip-flops is determined from the number of states needed in the circuit and the choice of state assignment codes

- → Once the type and number of flip-flops are determined, the design process involves a transformation from a sequential circuit problem into a combinational circuit problem.

# The procedure for designing synchronous sequential circuits can be summarized by a list of recommended steps:

- 1. From the word description and specifications of the desired operation, derive a state diagram for the circuit.

- 2. Reduce the number of states if necessary.

- 3. Assign binary values to the states.

- 4. Obtain the binary-coded state table.

- 5. Choose the type of flip-flops to be used.

- 6. Derive the simplified flip-flop input equations and output equations.

- 7. Draw the logic diagram.

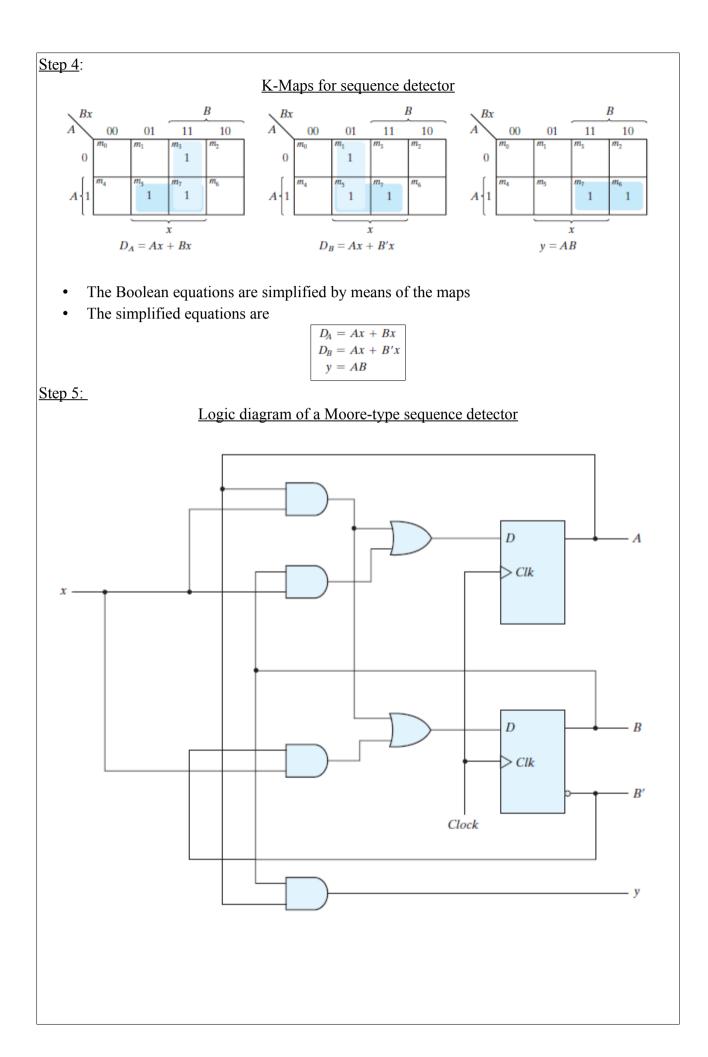

# a) Synthesis Using D Flip-Flops

#### Example:

• To design a circuit that detects a sequence of three or more consecutive 1's in a string of bits coming through an input line

<u>Step 1:</u>

State diagram for sequence detector

- Starting with state S0, the reset state.

- If the input is 0, the circuit stays in S0,

- If the input is 1, it goes to state S1 to indicate that a 1 was detected.

- If the next input is 1, the change is to state S2 to indicate the arrival of two consecutive 1's,

- If the input is 0, the state goes back to S0.

- The third consecutive 1 sends the circuit to state S3.

- If more 1's are detected, the circuit stays in S3.

- Any 0 input sends the circuit back to S0.

- ✓ In this way, the circuit stays in S3 as long as there are three or more consecutive 1's received.

- ✓ This is a Moore model sequential circuit, since the output is 1 when the circuit is in state S3 and is 0 otherwise.

<u>Step 2:</u>

#### a) Synthesis Using D Flip-Flops

• Assign binary codes to the states and list the state table. *State Table for Sequence Detector*

| Present<br>State |   | Input | Ne<br>Sta | xt<br>ate | Output |  |  |

|------------------|---|-------|-----------|-----------|--------|--|--|

| Α                | В | x     | Α         | В         | У      |  |  |

| 0                | 0 | 0     | 0         | 0         | 0      |  |  |

| 0                | 0 | 1     | 0         | 1         | 0      |  |  |

| 0                | 1 | 0     | 0         | 0         | 0      |  |  |

| 0                | 1 | 1     | 1         | 0         | 0      |  |  |

| 1                | 0 | 0     | 0         | 0         | 0      |  |  |

| 1                | 0 | 1     | 1         | 1         | 0      |  |  |

| 1                | 1 | 0     | 0         | 0         | 1      |  |  |

| 1                | 1 | 1     | 1         | 1         | 1      |  |  |

#### <u>Step 3:</u>

- Choose two D flip-flops to represent the four states,

- Label their outputs A and B.

- one input x

- one output y.

- ✓ The characteristic equation of the D flip-flop is  $Q(t + 1) = D_Q$

$\rightarrow$  the next-state values in the state table specify the D input condition for the flip-flop.

✓ The flip-flop input equations can be obtained directly from the next-state columns of A and B and expressed in sum-of-minterms form as

$$A(t + 1) = D_A(A, B, x) = \Sigma(3, 5, 7)$$

$$B(t + 1) = D_B(A, B, x) = \Sigma(1, 5, 7)$$

$$y(A, B, x) = \Sigma(6, 7)$$

- A, B present-state values of flip-flops A and B,

- x input

$D_A$ ,  $D_B$  -input equations.

y - output

• The minterms for output y are obtained from the output column in the state table.

# **Excitation Tables**

- D-type flip-flops

- $\circ$   $\;$  The input equations are obtained directly from the next state.

- JK and T types of flip-flops

- In order to determine the input equations for these flip-flops, it is necessary to derive a functional relationship between the state table and the input equations.

Excitation Table for J-K Flip-flop:

| <b>Q</b> ( <i>t</i> ) | Q(t=1) | J | K |

|-----------------------|--------|---|---|

| 0                     | 0      | 0 | Х |

| 0                     | 1      | 1 | Х |

| 1                     | 0      | X | 1 |

| 1                     | 1      | Х | 0 |

- $\checkmark$  There are four possible transitions from the present state to the next state.

- ✓ The required input conditions for each of the four transitions are derived from the information available in the characteristic table.

- ✓ The symbol X in the tables represents a don't-care condition, which means that it does not matter whether the input is 1 or 0.

- ✓ When both present state and next state are 0, the J input must remain at 0 and the K input can be either 0 or 1.

- ✓ Similarly, when both present state and next state are 1, the K input must remain at 0, while the J input can be 0 or 1.

- ✓ If the flip-flop is to have a transition from the 0-state to the 1-state, J must be equal to 1, since the J input sets the flip-flop.

- ✓ Input K may be either 0 or 1. If K = 0, the J = 1 condition sets the flip-flop as required;

- ✓ If K = 1 and J = 1, the flip-flop is complemented and goes from the 0-state to the 1-state as required.

- ✓ Therefore, the K input is marked with a don't-care condition for the 0-to-1 transition.

- ✓ For a transition from the 1-state to the 0-state, we must have K = 1, since the K input clears the flip-flop. However, the J input may be either 0 or 1, since J = 0 has no effect and J = 1 together with K = 1 complements the flip-flop with a resultant transition from the 1-state to the 0-state.

Excitation table for the T flip-flop:

| <b>Q(t)</b> | Q(t=1) | T |

|-------------|--------|---|

| 0           | 0      | 0 |

| 0           | 1      | 1 |

| 1           | 0      | 1 |

| 1           | 1      | 0 |

- From the characteristic table,

- when input T = 1, the state of the flip-flop is complemented, and

- when T = 0, the state of the flip-flop remains unchanged.

- ✓ when the state of the flip-flop must remain the same, the requirement is that T = 0.

- $\checkmark$  When the state of the flip-flop has to be complemented, T must equal 1.

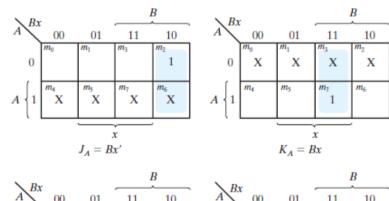

# b) Synthesis Using JK Flip-Flops

# Example:

| tate T | able | and | IK Fli | p-Flop | Inputs |  |

|--------|------|-----|--------|--------|--------|--|

|   | sent<br>ate | Input |   | Next<br>State Flip-Flop Ing |                |                | Flip-Flop Input |                |  |

|---|-------------|-------|---|-----------------------------|----------------|----------------|-----------------|----------------|--|

| Α | В           | x     | Α | В                           | J <sub>A</sub> | K <sub>A</sub> | J <sub>B</sub>  | K <sub>B</sub> |  |

| 0 | 0           | 0     | 0 | 0                           | 0              | Х              | 0               | Х              |  |

| 0 | 0           | 1     | 0 | 1                           | 0              | Х              | 1               | Х              |  |

| 0 | 1           | 0     | 1 | 0                           | 1              | Х              | Х               | 1              |  |

| 0 | 1           | 1     | 0 | 1                           | 0              | Х              | Х               | 0              |  |

| 1 | 0           | 0     | 1 | 0                           | Х              | 0              | 0               | Х              |  |

| 1 | 0           | 1     | 1 | 1                           | Х              | 0              | 1               | Х              |  |

| 1 | 1           | 0     | 1 | 1                           | Х              | 0              | Х               | 0              |  |

| 1 | 1           | 1     | 0 | 0                           | Х              | 1              | Х               | 1              |  |

Step 1:

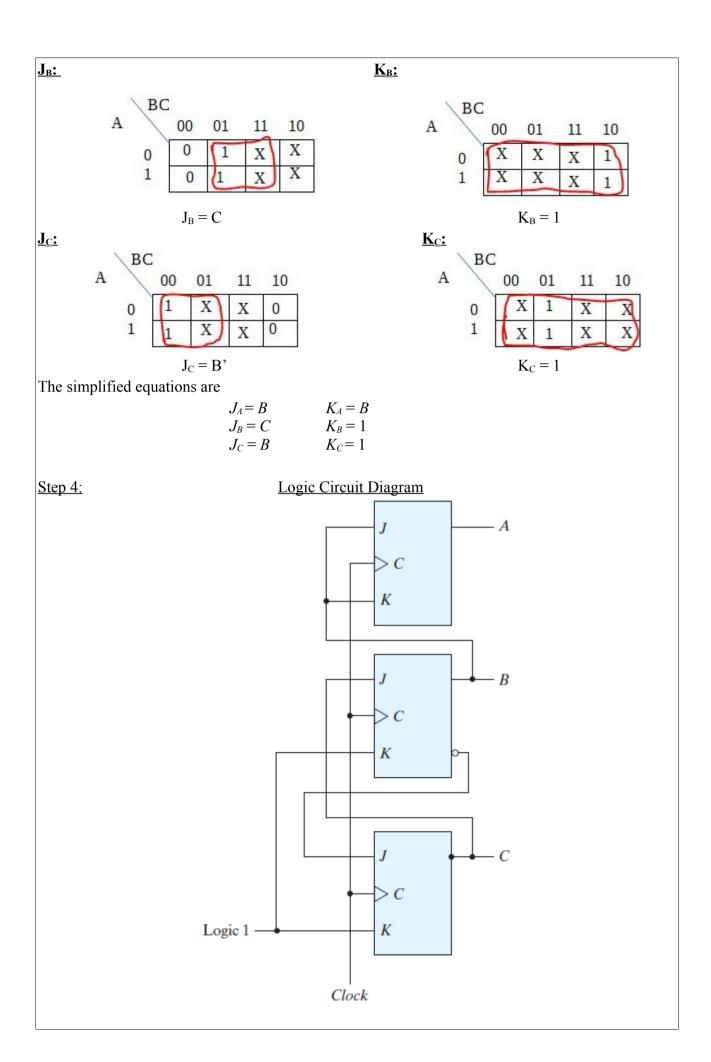

## Maps for J and K input equations

<u>Step 2:</u>

# Logic diagram for sequential circuit with JK flip-flops

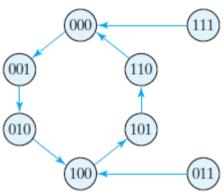

#### c) Synthesis Using T Flip-Flops

#### Example:

- Designing a binary counter.

- An n-bit binary counter consists of n flip-flops that can count in binary from 0 to  $2^n 1$ .

- ✓ Binary states indicated inside the circles,

- ✓ The flip-flop outputs repeat the binary count sequence with a return to 000 after 111.

- ✓ The directed lines between circles are not marked with input and output values as in other state diagrams.

- ✓ State transitions in clocked sequential circuits are initiated by a clock edge;

- $\checkmark$  the flip-flops remain in their present states if no clock is applied.

- ✓ The only input to the circuit is the clock, and the outputs are specified by the present state of the flip-flops.

- ✓ The next state of a counter depends entirely on its present state, and the state transition occurs every time the clock goes through a transition.

| Pres           | sent S                | tate | Ne             | Next State |    | Flip-           | Flop Iı         | nputs           |

|----------------|-----------------------|------|----------------|------------|----|-----------------|-----------------|-----------------|

| A <sub>2</sub> | <i>A</i> <sub>1</sub> | Ao   | A <sub>2</sub> | <b>A</b> 1 | Ao | T <sub>A2</sub> | T <sub>A1</sub> | T <sub>A0</sub> |

| 0              | 0                     | 0    | 0              | 0          | 1  | 0               | 0               | 1               |

| 0              | 0                     | 1    | 0              | 1          | 0  | 0               | 1               | 1               |

| 0              | 1                     | 0    | 0              | 1          | 1  | 0               | 0               | 1               |

| 0              | 1                     | 1    | 1              | 0          | 0  | 1               | 1               | 1               |

| 1              | 0                     | 0    | 1              | 0          | 1  | 0               | 0               | 1               |

| 1              | 0                     | 1    | 1              | 1          | 0  | 0               | 1               | 1               |

| 1              | 1                     | 0    | 1              | 1          | 1  | 0               | 1               | 1               |

| 1              | 1                     | 1    | 0              | 0          | 0  | 1               | 1               | 1               |

#### <u>Step 1:</u>

- The three flip-flops are symbolized by A2, A1, and A0.

- Binary counters are constructed most efficiently with T flip-flops because of their complement property. The flip-

#### **Registers and Counters**

- ✓ Registers

- Shift Registers 1

- A clocked sequential circuit consists of a group of flip-flops and combinational gates.

- Circuits that include flip-flops are usually classified by the function they perform •

- Two such circuits are

- 0 registers and

- 0 counters.

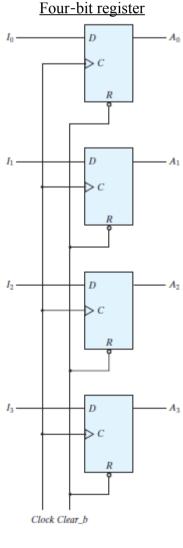

- A register is a group of flip-flops, each one of which shares a common clock and is capable of storing one bit of information.

- An n-bit register consists of a group of n flip-flops capable of storing n bits of binary information.

- In addition to the flip-flops, a register may have combinational gates that perform certain data-processing tasks.

- The flip-flops hold the binary information, and the gates determine how the information is transferred into the register.

- The common clock input triggers all flip-flops on the positive edge of each pulse, and the binary data available at the four inputs are transferred into the register.

- The value of  $(I_3, I_2, I_1, I_0)$  immediately before the clock edge determines the value of  $(A_3, A_2, A_1, A_0)$  after the clock edge.

- The four outputs can be sampled at any time to obtain the binary information stored in the register.

- The input Clear\_b goes to the active-low R (reset) input of all four flip-flops.

- When this input goes to 0, all flip-flops are reset asynchronously.

- The Clear\_b input is useful for clearing the register to all 0's prior to its clocked operation.

- The R inputs must be maintained at logic 1 (i.e., de-asserted) during normal clocked operation

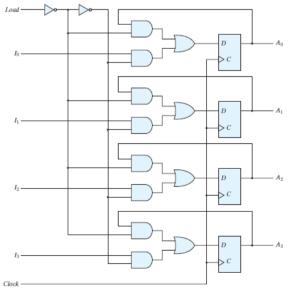

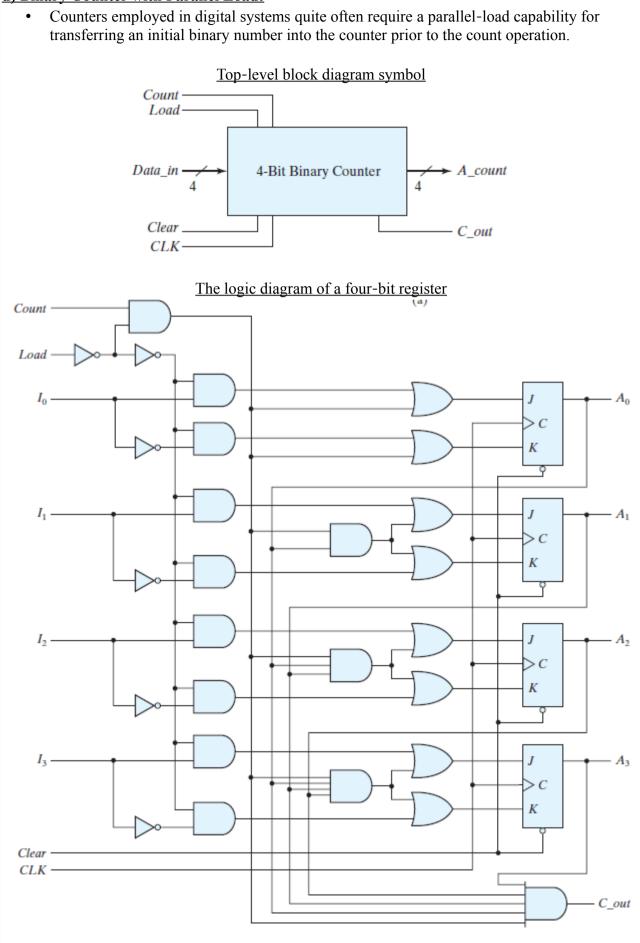

# **Register with Parallel Load**

- Registers with parallel load are a fundamental building block in digital systems.

- Synchronous digital systems have a master clock generator that supplies a continuous train of clock pulses.

- The pulses are applied to all flip-flops and registers in the system.

- The master clock acts like a drum that supplies a constant beat to all parts of the system.

- A separate control signal must be used to decide which register operation will execute at each clock pulse.

- The transfer of new information into a register is referred to as loading or updating the register.

- If all the bits of the register are loaded simultaneously with a common clock pulse, then loading is done in parallel.

- A clock edge applied to the C inputs of the register, load all four inputs in parallel.

- To fully synchronize the system, ensure that all clock pulses arrive at the same time anywhere in the system, so that all flip-flops trigger simultaneously.

# Four-bit register with parallel load

• A four-bit data-storage register with a load control input that is directed through gates and into the D inputs of the flip-flops

- The additional gates implement a two-channel mux whose output drives the input to the register with either the data bus or the output of the register.

- The load input to the register determines the action to be taken with each clock pulse.

- When the load input is 1, the data at the four external inputs are transferred into the register with the next positive edge of the clock.

- When the load input is 0, the outputs of the flip-flops are connected to their respective inputs.

- The feedback connection from output to input is necessary because a D flip-flop does not have a "no change" condition.

- With each clock edge, the D input determines the next state of the register.

- To leave the output unchanged, it is necessary to make the D input equal to the present value of the output

- The transfer of information from the data inputs or the outputs of the register is done simultaneously with all four bits in response to a clock edge.

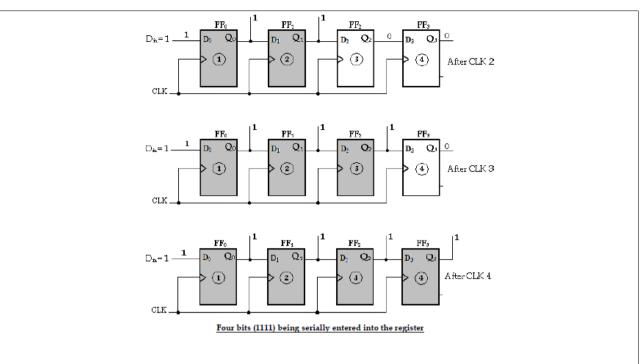

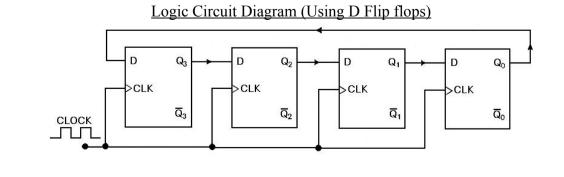

# SHIFT REGISTERS

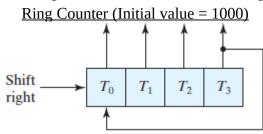

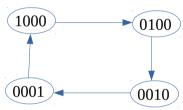

- → A register capable of shifting the binary information held in each cell to its neighboring cell, in a selected direction, is called a shift register.

- → The logical configuration of a shift register consists of a chain of flip-flops in cascade, with the output of one flip-flop connected to the input of the next flip-flop.

- → All flip-flops receive common clock pulses, which activate the shift of data from one stage to the next. The simplest possible shift register is one that uses only flip-flops

- The output of a given flip-flop is connected to the D input of the flip-flop at its right.

- This shift register is unidirectional (left-to-right).

- Each clock pulse shifts the contents of the register one bit position to the right.

- The configuration does not support a left shift.

- The serial input determines what goes into the leftmost flip-flop during the shift.

- The serial output is taken from the output of the rightmost flip-flop the clock's signal can be suppressed by gating the clock signal to prevent the register from shifting.

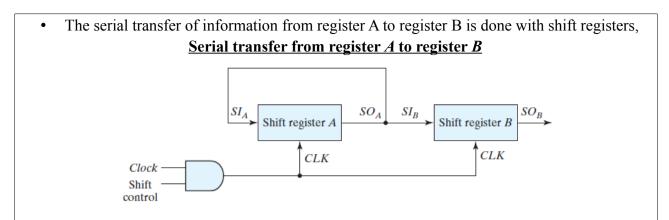

# a) Serial Transfer:

- The datapath of a digital system is said to operate in serial mode when information is transferred and manipulated one bit at a time.

- Information is transferred one bit at a time by shifting the bits out of the source register and into the destination register.

- parallel transfer all the bits of the register are transferred at the same time.

- The serial output (SO) of register A is connected to the serial input (SI) of register B.

- To prevent the loss of information stored in the source register, the information in register A is made to circulate by connecting the serial output to its serial input.

- The initial content of register B is shifted out through its serial output and is lost unless it is transferred to a third shift register.

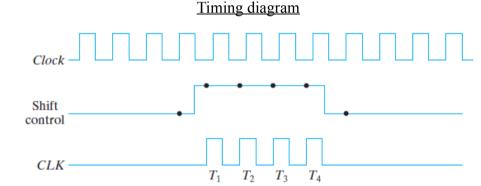

- The shift control input determines when and how many times the registers are shifted.

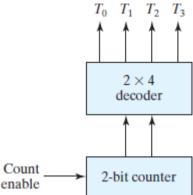

- an AND gate that allows clock pulses to pass into the CLK terminals only when the shift control is active the shift registers have four bits each.

- Then the control unit that supervises the transfer of data must be designed in such a way that it enables the shift registers, through the shift control signal, for a fixed time of four clock pulses in order to pass an entire word

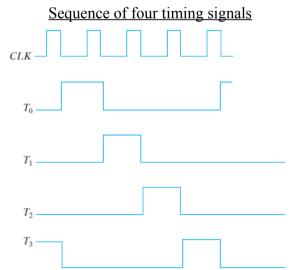

- ✓ The shift control signal is synchronized with the clock and changes value just after the negative edge of the clock.

- ✓ The next four clock pulses find the shift control signal in the active state, so the output of the AND gate connected to the CLK inputs produces four pulses: T₁, T₂, T₃, and T₄.

- ✓ Each rising edge of the pulse causes a shift in both registers.

- $\checkmark$  The fourth pulse changes the shift control to 0, and the shift registers are disabled.

# Example:

- The binary content of A before the shift is 1011 and that of B is 0010.

- The serial transfer from A to B occurs in four steps

| Timing Pulse  | Shift Register A |   |   | Shift Register B |   |   |   |   |

|---------------|------------------|---|---|------------------|---|---|---|---|

| Initial value | 1                | 0 | 1 | 1                | 0 | 0 | 1 | 0 |

| After $T_1$   | 1                | 1 | 0 | 1                | 1 | 0 | 0 | 1 |

| After $T_2$   | 1                | 1 | 1 | 0                | 1 | 1 | 0 | 0 |

| After $T_3$   | 0                | 1 | 1 | 1                | 0 | 1 | 1 | 0 |

| After $T_4$   | 1                | 0 | 1 | 1                | 1 | 0 | 1 | 1 |

- → With the first pulse, T<sub>1</sub>, the rightmost bit of A is shifted into the leftmost bit of B and is also circulated into the leftmost position of A.

- $\rightarrow$  At the same time, all bits of A and B are shifted one position to the right.

- → The previous serial output from B in the rightmost position is lost, and its value changes from 0 to 1.

- → The next three pulses perform identical operations, shifting the bits of A into B, one at a time.

- → After the fourth shift, the shift control goes to 0, and registers A and B both have the value 1011.

- → The contents of A are copied into B, so that the contents of A remain unchanged i.e., the contents of A are restored to their original value.

- In the parallel mode, information is available from all bits of a register and all bits can be transferred simultaneously during one clock pulse.

- > In the serial mode, the registers have a single serial input and a single serial output.

- The information is transferred one bit at a time while the registers are shifted in the same direction.

# b) Serial Addition:

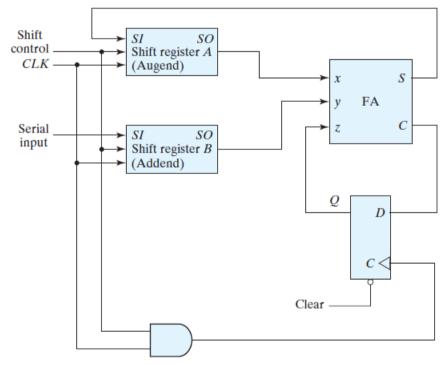

- The two binary numbers to be added serially are stored in two shift registers.

- Beginning with the least significant pair of bits, the circuit adds one pair at a time through a single full-adder (FA) circuit

- The carry out of the full adder is transferred to a D flip-flop, the output of which is then used as the carry input for the next pair of significant bits.

- The sum bit from the S output of the full adder could be transferred into a third shift register.

- By shifting the sum into A while the bits of A are shifted out, it is possible to use one register for storing both the augend and the sum bits.

- The serial input of register B can be used to transfer a new binary number while the addend bits are shifted out during the addition.

- → <u>The operation of the serial adder is as follows:</u>

- Initially, register A holds the augend, register B holds the addend, and the carry flip-flop is cleared to 0.

- The outputs (SO) of A and B provide a pair of significant bits for the full adder at x and y.

- Output Q of the flip-flop provides the input carry at z.

- The shift control enables both registers and the carry flip-flop, so at the next clock pulse, both registers are shifted once to the right, the sum bit from S enters the leftmost flip-flop of A, and the output carry is transferred into flip-flop Q.

- The shift control enables the registers for a number of clock pulses equal to the number of bits in the registers.

- For each succeeding clock pulse, a new sum bit is transferred to A, a new carry is transferred to Q, and both registers are shifted once to the right.

- This process continues until the shift control is disabled.

- The addition is accomplished by passing each pair of bits together with the previous carry through a single full-adder circuit and transferring the sum, one bit at a time, into register A.

- Initially, register A and the carry flip-flop are cleared to 0, and then the first number is added from B.

- While B is shifted through the full adder, a second number is transferred to it through its serial input.

- The second number is then added to the contents of register A, while a third number is transferred serially into register B.

- This can be repeated to perform the addition of two, three, or more four-bit numbers and accumulate their sum in register A.

- ✓ The parallel adder uses registers with a parallel load, whereas the serial adder uses shift registers.

- ✓ The number of full-adder circuits in the parallel adder is equal to the number of bits in the binary numbers, whereas the serial adder requires only one full-adder circuit and a carry flip-flop.

- ✓ Excluding the registers, the parallel adder is a combinational circuit, whereas the serial adder is a sequential circuit which consists of a full adder and a flip-flop that stores the output carry.

| Present State | Inp | outs | Next State | Output | Flip-Flo | p Inputs |

|---------------|-----|------|------------|--------|----------|----------|

| Q             | x   | y    | Q          | S      | JQ       | Kq       |

| 0             | 0   | 0    | 0          | 0      | 0        | Х        |

| 0             | 0   | 1    | 0          | 1      | 0        | Х        |

| 0             | 1   | 0    | 0          | 1      | 0        | Х        |

| 0             | 1   | 1    | 1          | 0      | 1        | Х        |

| 1             | 0   | 0    | 0          | 1      | Х        | 1        |

| 1             | 0   | 1    | 1          | 0      | Х        | 0        |

| 1             | 1   | 0    | 1          | 0      | Х        | 0        |

| 1             | 1   | 1    | 1          | 1      | Х        | 0        |

The state table that specifies the sequential circuit

- The present state of Q is the present value of the carry.

- The present carry in Q is added together with inputs x and y to produce the sum bit in output S.

- The next state of Q is equal to the output carry.

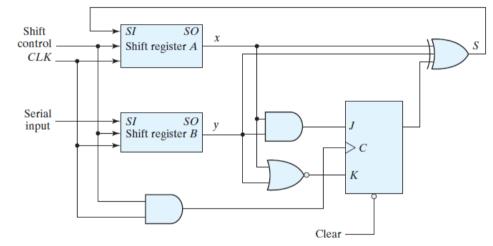

- If a D flip-flop is used for Q, the circuit reduces to the one

- ➔ If a JK flipflop is used for Q, it is necessary to determine the values of inputs J and K by referring to the excitation table

- → The two flip-flop input equations and the output equation can be simplified by means of maps to

$$J_Q = xy$$

$$K_Q = x'y' = (x + y)'$$

$$S = x \oplus y \oplus Q$$

Second form of serial adder

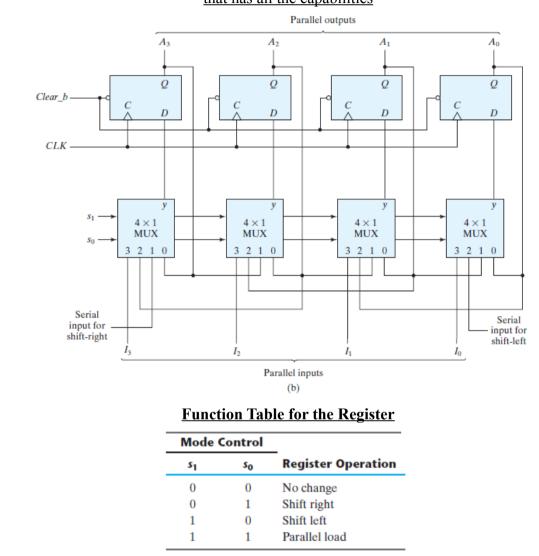

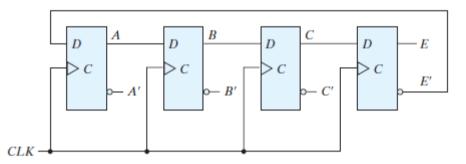

# c) Universal Shift Register:

- If the flip-flop outputs of a shift register are accessible, then information entered serially by shifting can be taken out in parallel from the outputs of the flip-flops.

- If a parallel load capability is added to a shift register, then data entered in parallel can be taken out in serial fashion by shifting the data stored in the register.

- Some shift registers provide the necessary input and output terminals for parallel transfer.

- <u>Shift register has the following capabilities</u>:

- 1. A clear control to clear the register to 0.

- 2. A clock input to synchronize the operations.

- 3. A shift-right control to enable the shift-right operation and the serial input and output lines associated with the shift right.

- 4. A shift-left control to enable the shift-left operation and the serial input and output lines associated with the shift left.

- 5. A parallel-load control to enable a parallel transfer and the n input lines associated with the parallel transfer.

- 6. n parallel output lines.

- 7. A control state that leaves the information in the register unchanged in response to the clock. Other shift registers may have only some of the preceding functions, with at least one shift operation.

- A register capable of shifting in one direction only is a unidirectional shift register.

- One that can shift in both directions is a bidirectional shift register.

- If the register has both shifts and parallel-load capabilities, it is referred to as a universal shift register.

The block diagram symbol and the circuit diagram of a four-bit universal shift register that has all the capabilities

- → When s1s0 = 01, terminal 1 of the multiplexer inputs has a path to the D inputs of the flipflops. This causes a shift-right operation, with the serial input transferred into flip-flop A3.

- → When s1s0 = 10, a shift-left operation results, with the other serial input going into flip-flop A0.

- → Finally, when s1s0 = 11, the binary information on the parallel input lines is transferred into the register simultaneously during the next clock edge.

- It is more economical to use a single line and transmit the information serially, one bit at a time.

- The transmitter accepts the n -bit data in parallel into a shift register and then transmits the data serially along the common line.

- The receiver accepts the data serially into a shift register.

- When all n bits are received, they can be taken from the outputs of the register in parallel.

• The transmitter performs a parallel-to-serial conversion of data and the receiver does a serial-to-parallel conversion.

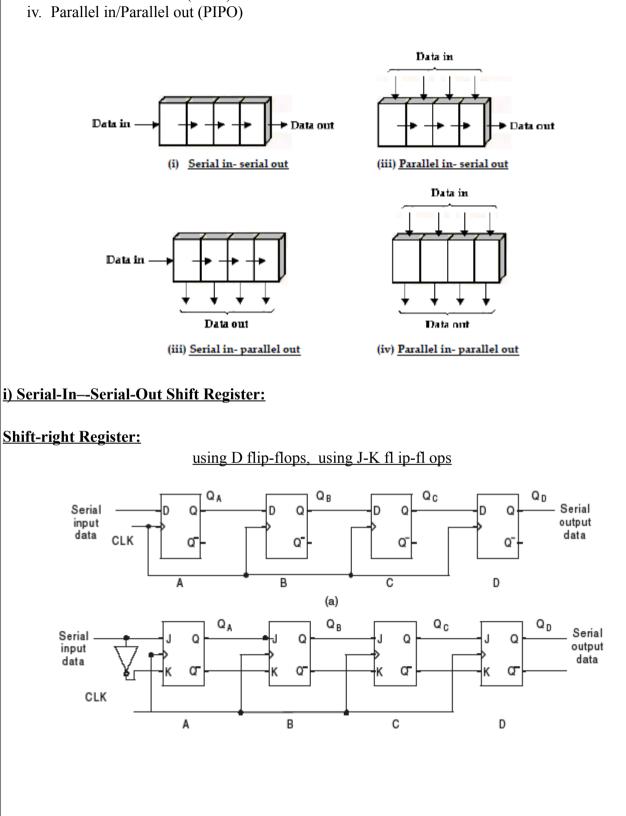

#### d) Types of Shift Register:

- i. Serial in/Serial out (SISO)

- ii. Serial in/Parallel out (SIPO)

- iii. Parallel in/Serial out (PISO)

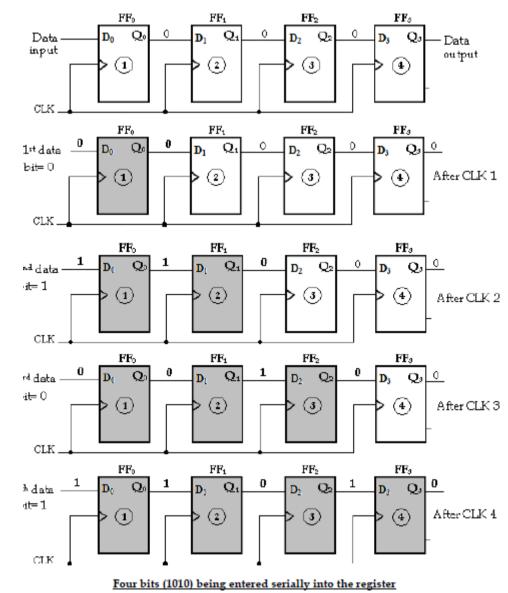

#### **Operation of the Shift-right Register:**

- 1. To shift a 1 into the flip-flop, J = 1 and K = 0,

- 2. To shift a 0 into the flip-flop, J = 0 and K = 1.

| Timing pulse                      | $Q_{A}$ | $Q_B$         | $Q_c$      | $Q_D$ | Serial output at $Q_D$ |

|-----------------------------------|---------|---------------|------------|-------|------------------------|

| Initial value                     | ~       | 0             | 0          | 0     | 0                      |

| After 1 <sup>st</sup> clock pulse | 1       | <b>&gt;</b> 0 | <b>A</b> 0 | ▲0    | 0                      |

| After 2 <sup>nd</sup> clock pulse | 1       | 1             | 0          | 0     | 0                      |

| After 3 <sup>rd</sup> clock pulse | 0       | 1             | 1          | 0     | 0                      |

| After 4 <sup>th</sup> clock pulse | 1       | 0             | 1          | 1     | 1                      |

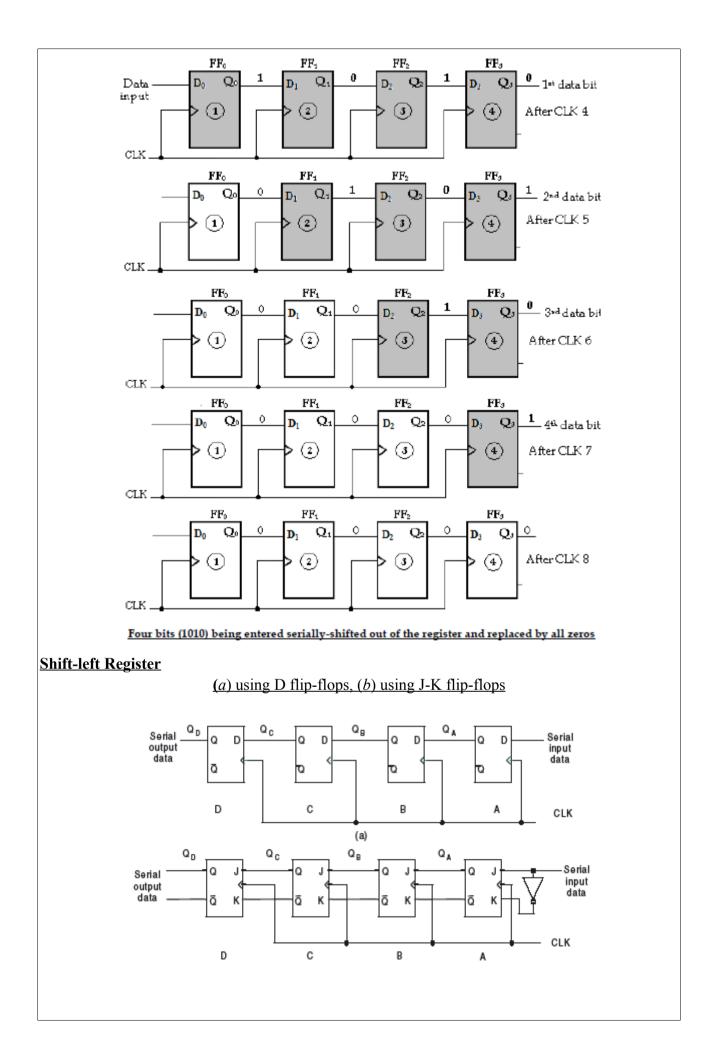

# Example: The entry of the four bits 1010 into the register - Illustration

#### **Operation of the Shift-left Register**

| Timing pulse                      | $Q_D$ | $Q_c$      | $Q_B$    | $Q_{A}$  | Serial output at $Q_D$ |

|-----------------------------------|-------|------------|----------|----------|------------------------|

| Initial value                     | 0     | <b>∕</b> ⁰ | <u> </u> | <u> </u> | 0                      |

| After 1 <sup>st</sup> clock pulse | 0     | 0          | 0        | 0        | 0                      |

| After 2 <sup>nd</sup> clock pulse | 0     | 0          | 0        | 1        | 0                      |

| After 3 <sup>rd</sup> clock pulse | 0     | 0          | 1        | 1        | 0                      |

| After 4 <sup>th</sup> clock pulse | 0     | 1          | 1        | 1        | 0                      |

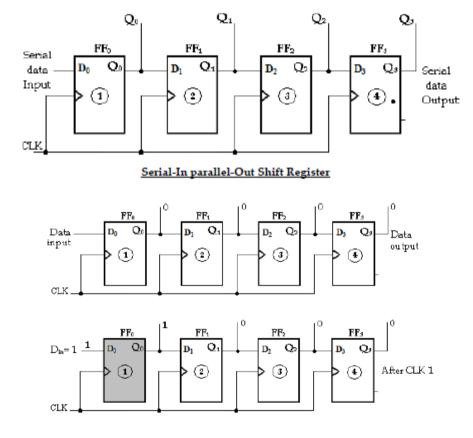

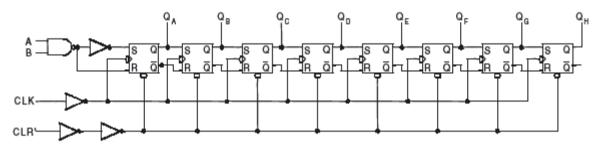

#### ii) Serial-In–Parallel-Out Register:

- Data bits are entered into the register in the same as serial-in serial-out shift register.

- But the output is taken in parallel.

- Once the data are stored, each bit appears on its respective output line and all bits are available simultaneously instead of on a bit-by-bit.

# <u> 8-bit shift register – Logic Diagram</u>

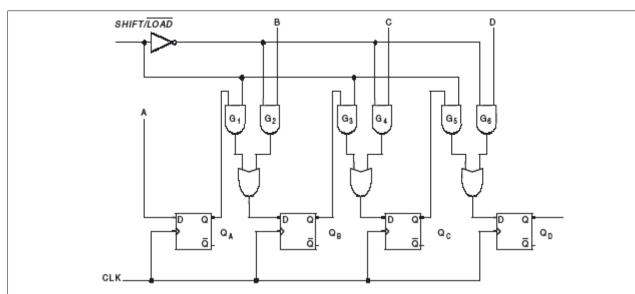

#### iii) Parallel-In–Serial-Out Register:

- the bits are entered in parallel i.e., simultaneously into their respective stages on parallel lines.

- There are four data input lines, X0, X1, X2 and X3 for entering data in parallel into the register.

- SHIFT/ LOAD input is the control input, which allows four bits of data to load in parallel into the register.

- When SHIFT/LOAD is LOW, gates G1, G2, G3 and G4 are enabled, allowing each data bit to be applied to the D input of its respective Flip-Flop.

- When a clock pulse is applied, the Flip-Flops with D = 1 will set and those with D = 0 will reset, thereby storing all four bits simultaneously.

- When SHIFT/LOAD is HIGH, gates G1, G2, G3 and G4 are disabled and gates G5, G6 and G7 are enabled, allowing the data bits to shift right from one stage to the next.

- The OR gates allow either the normal shifting operation or the parallel data-entry operation, depending on which AND gates are enabled by the level on the SHIFT/LOAD input.

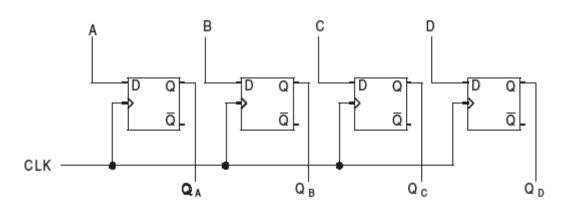

#### iv) Parallel-In–Parallel-Out Register:

• In this type, there is simultaneous entry of all data bits and the bits appear on parallel outputs simultaneously.

#### **Counters:**

- A register that goes through a prescribed sequence of states upon the application of input pulses is called a counter.

- A counter is essentially a register that goes through a predetermined sequence of binary states.

- The input pulses may be clock pulses, or they may originate from some external source and may occur at a fixed interval of time or at random.

- The sequence of states may follow the binary number sequence or any other sequence of states.

- The gates in the counter are connected in such a way as to produce the prescribed sequence of states.

- **x** Various types of registers are available commercially.

- The simplest register is one that consists of only flip-flops, without any gates.

- A counter that follows the binary number sequence is called a binary counter .

- An n -bit binary counter consists of n flip-flops and can count in binary from 0 through 2n 1.

#### Counters are available in two categories:

- 1. Ripple counters (Asynchronous Counters)

- 2. Synchronous counters.

## 1. <u>Ripple counters:</u>

• In a ripple counter, a flip-flop output transition serves as a source for triggering other flipflops.

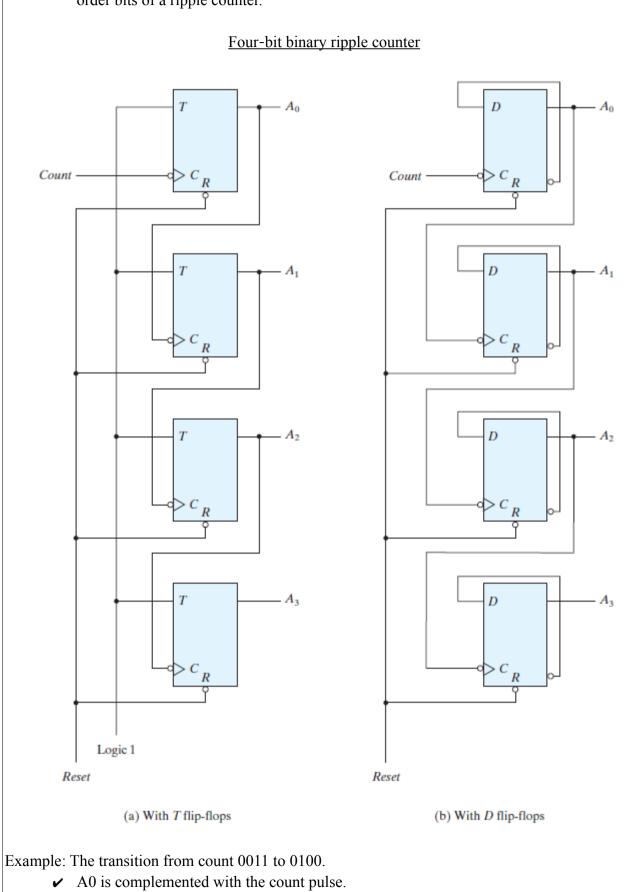

#### <u>a) Binary Ripple Counter</u>

- The count starts with binary 0 and increments by 1 with each count pulse input.

- After the count of 15, the counter goes back to 0 to repeat the count.

| <u>Bin</u>     | Binary Count Sequence |                |    |  |  |  |  |  |  |

|----------------|-----------------------|----------------|----|--|--|--|--|--|--|

| A <sub>3</sub> | A <sub>2</sub>        | A <sub>1</sub> | Ao |  |  |  |  |  |  |

| 0              | 0                     | 0              | 0  |  |  |  |  |  |  |

| 0              | 0                     | 0              | 1  |  |  |  |  |  |  |

| 0              | 0                     | 1              | 0  |  |  |  |  |  |  |

| 0              | 0                     | 1              | 1  |  |  |  |  |  |  |

| 0              | 1                     | 0              | 0  |  |  |  |  |  |  |

| 0              | 1                     | 0              | 1  |  |  |  |  |  |  |

| 0              | 1                     | 1              | 0  |  |  |  |  |  |  |

| 0              | 1                     | 1              | 1  |  |  |  |  |  |  |

| 1              | 0                     | 0              | 0  |  |  |  |  |  |  |

- ✓ A binary ripple counter consists of a series connection of complementing flip-flops, with the output of each flip-flop connected to the C input of the next higher order flip-flop.

- ✓ The flip-flop holding the least significant bit receives the incoming count pulses

- $\checkmark$  Every time that A0 goes from 1 to 0, it complements A1.

- $\checkmark$  Every time that A1 goes from 1 to 0, it complements A2.

- ✓ Every time that A2 goes from 1 to 0, it complements A3 and so on for any other higher order bits of a ripple counter.

- ✓ Since A0 goes from 1 to 0, it triggers A1 and complements it.

- ✓ As a result, A1 goes from 1 to 0, which in turn complements A2, changing it from 0 to 1.

- ✓ A2 does not trigger A3, because A2 produces a positive transition and the flip-flop responds only to negative transitions.

- ✓ Thus, the count from 0011 to 0100 is achieved by changing the bits one at a time, so the count goes from 0011 to 0010, then to 0000, and finally to 0100.

- ✓ The flip-flops change one at a time in succession, and the signal propagates through the counter in a ripple fashion from one stage to the next.

- The output of each flip-flop is connected to the C input of the next flip-flop in sequence.

- The flip-flop holding the least significant bit receives the incoming count pulses.

- The T inputs of all the flip-flops in (a) are connected to a permanent logic 1, making each flip-flop complement if the signal in its C input goes through a negative transition.

- The bubble in front of the dynamic indicator symbol next to C indicates that the flip-flops respond to the negative-edge transition of the input.

- The negative transition occurs when the output of the previous flip-flop to which C is connected goes from 1 to 0.

# b) Binary countdown counter:

- A binary counter with a reverse count is called a binary countdown counter .

- ✓ In a countdown counter, the binary count is decremented by 1 with every input count pulse.

- ✓ The count of a four-bit countdown counter starts from binary 15 and continues to binary counts 14, 13, 12, ..., 0 and then back to 15.

- ✓ A list of the count sequence of a binary countdown counter shows that the least significant bit is complemented with every count pulse.

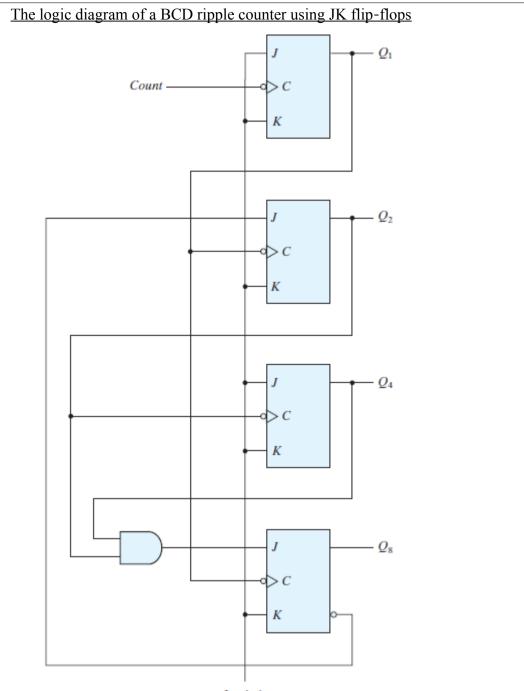

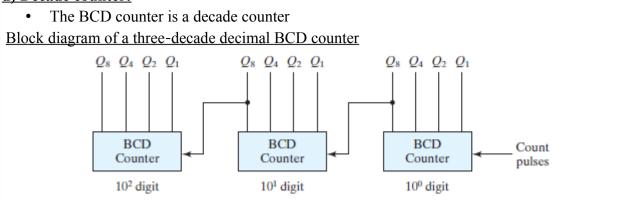

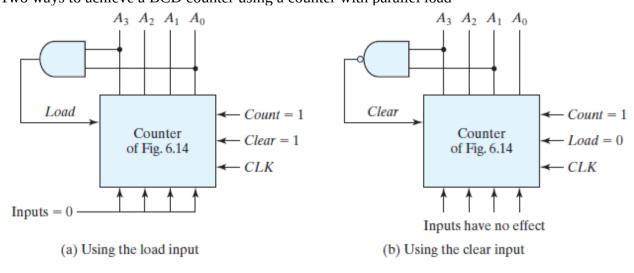

# c) BCD Ripple Counter:

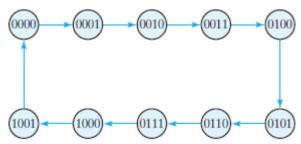

- A decimal counter follows a sequence of 10 states and returns to 0 after the count of 9.

- A counter must have at least four flip-flops to represent each decimal digit, since a decimal digit is represented by a binary code with at least four bits.

- The sequence of states in a decimal counter is dictated by the binary code used to represent a decimal digit.

State diagram of a decimal BCD counter

• A decimal counter is similar to a binary counter, except that the state after 1001 (the code for decimal digit 9) is 0000 (the code for decimal digit 0).

Logic 1

- The four outputs are designated by the letter symbol Q, with a numeric subscript equal to the binary weight of the corresponding bit in the BCD code.

- The output of Q1 is applied to the C inputs of both Q2 and Q8 and the output of Q2 is applied to the C input of Q4.

- The J and K inputs are connected either to a permanent 1 signal or to outputs of other flip-flops.

- Signals that affect the flip-flop transition depend on the way they change from 1 to 0.

- The operation of the counter can when the C input goes from 1 to 0, the flip-flop is

- set if J = 1

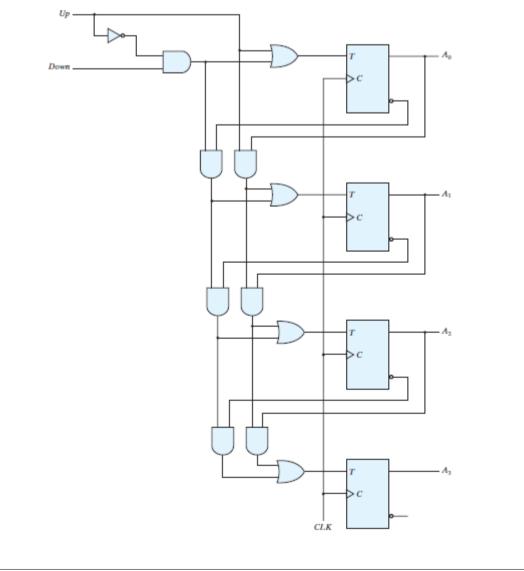

- cleared if K = 1,